日前才正式发表新一代显示卡的绘图芯片大厂辉达 (NVIDIA),日前又公告未来绘图芯片的发展路线图。其中,针对再下一代的代号 Ampere 的显示卡,除了制程将升级到 7 纳米节点之外,虽然性能还是未知数,但是藉由 7 纳米制程技术将会把绘图芯片的芯片核心面积大幅降低,从现在 754㎜² 的 GV102 或者 TU102 的核心面积,将降低到 440㎜² 左右的核心面积。

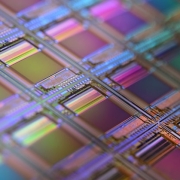

根据国外科技网站《3DCenter》日前的报导指出,在 NVIDIA 自 2016 年到 2020 年的绘图芯片路线图中,可以看出当前 Volta 及 Turing 的 12纳米制程芯片,以及未来的 Ampere 的 7 纳米制程芯片发展。其中,在 12 纳米制程的 Volta 与 Turing 芯片中,目前主要有 3 种核心。GV100 的核心面积高达 815㎜²。而 GV102,也就是现在的 TU102 核心是 754㎜²。至于 GV014,也就是才刚发表的 TU104 核心面积,估算是来到 500㎜² 左右。

而在这样的核心架构下,虽然 12 纳米制程节点的绘图芯片架构更适合高性能计算及 AI 运算,而且 Turing 架构的芯片还加入了游戏用的光线追踪功能。但是,总体来说还是 Volta 的架构,芯片核心面积比 Pascal 大,成本也很高,对主流市场上的低阶产品销售不利。

因此,游戏玩家还是在等待下一代的 7 纳米制程 Ampere 芯片。虽然,现在连影子都还没看到。不过,《3DCenter》网站根据 7 纳米制程的特点做了估算,使用新制程之后的绘图芯片核心面积将会大幅降低,GA100 会降至 550㎜² 左右,GA102核心降至 440㎜²,GA104 核心更只有 290㎜²。另外,在主流市场的 GA106 只有 190㎜²、GA107 则是 120㎜²,入门级的 GA108 核心只有 67㎜²。因此,可说 7 纳米绘图芯片核心面积较上一代下降了大概 30% 到 40%,这对降低成本以及制造难度都有其帮助。

另外,预计 NVIDIA 的 7 纳米制程绘图芯片也将是台积电代工。而且根据台积电的消息,与 16 纳米制程技术相比,台积电的 7 纳米制程技术将提升 35% 的性能,降低 65% 的能耗。同时晶体管密度是之前的三倍。台积电预计 2019 年初会推出内含 EUV 技术的 7 纳米 + 制程技术,晶体管密度将会再提升 20%,功耗降低 10%。届时也会把芯片的性能再提升,更适合用在高效能的图形运算上。