” 摩尔定律未死!” 这句话如果是 Intel 公司说的,一点都没有悬念,毕竟摩尔定律的提出者是 Intel 联合创始人,50 多年来 Intel 也是摩尔定律最坚定的捍卫者。不过今天这句话是台积电而非 Intel 说的,他们也要继续推动摩尔定律。

日前,台积电全球营销主管Godfrey Cheng在博客发布了一篇文章,他在文章中表示,摩尔定律并没有“死亡”,并透露了有关5nm EUV(N5P)的信息和一些人工智能的观点。

1965年,英特尔创始人之一戈登·摩尔提出摩尔定律,他认为,当价格不变时,集成电路上可容纳的元器件数量约每隔18至24个月就会增加一倍,性能也将提升一倍。

这一定律深深地影响了半导体行业,但随着近年来,芯片工艺技术越来越接近物理极限,芯片制程的研发需要投入巨大的成本和精力,业界也出现了“摩尔定律已死”的观点。

台积电作为全球最大的芯片代工厂商,摩尔定律的问题也与它息息相关。这次,该公司的全球营销主管Godfrey Cheng亲自谈论摩尔定律,一定程度上也代表了台积电对业界重要观点的态度。

以下是文章大致内容:

一、摩尔定律尚未过时

自从我加入台积电已经快3个月了。就像任何加入新公司的员工一样,这段时间以来,我一直在吸收大量的信息和数据。

我首先探究的关键话题之一就是摩尔定律,简单来说,就是集成器件或芯片中的晶体管数量大约每两年翻一番。

实际上,摩尔定律并不算是一种定律,而是一个能准确地描述半导体器件或芯片中晶体管数量的历史观察,或是未来预测的指南。

过去几十年来,这些观察和预测基本上是正确的。但随着新一轮十年的临近,一些人开始认为摩尔定律已经过时了。

多年来,在CPU和GPU技术的发展过程中,摩尔定律的观点是正确的。从20世纪70年代到21世纪初,晶体管时钟速度实现了从单兆赫到几千兆赫的爆炸性增长。

自2000年以来,芯片的计算性能大大提高。然而,它并不是通过提高晶体管时钟速度来实现的,而是将硅架构创新和计算工作负载进行线程化或并行化。

开发CPU和GPU的公司,通过进一步的架构创新,以及增加更多的计算核心来应对这种软件并行化。计算核心越多,芯片可处理的线程就越多,从而提供更高的整体性能。

二、N5P工艺将进一步提高芯片密度

通过上面的例子我们可以知道,芯片计算性能是通过在计算问题上投入更多的晶体管而提高的。那么,在同一区域置入更多晶体管的方法是什么?

是密度!摩尔定律是一个关于密度的观点,其密度指的是芯片特定二维区域中晶体管的数量。

为什么我们那么关心芯片面积?因为芯片面积与芯片成本成正比关系。摩尔在1965年发表的论文中清楚地表明,每个元件的制造成本与芯片上晶体管的总数之间存在一定的关联。

让我们探讨一下如今面临的一些计算问题,以及密度的提高将如何进一步提高芯片性能。

首先,有些人认为摩尔定律已经过时,是因为他们认为晶体管面积不可能再继续缩小了。在现代的晶体管规模中,典型的栅极大约有20纳米长,而水分子的直径只有2.75埃米或0.275纳米。

在这种规模下,许多因素限制了晶体管的制造。主要的挑战是人们要在原子水平上控制半导体材料。如何放置单个原子来制造晶体管?如何在现代芯片上发现数十亿个晶体管?如何以经济高效的方式制造这些拥有数十亿晶体管的芯片?

为了解决这个问题,台积电最近宣布了N5P制程节点,这不仅将进一步扩大我们在N5节点之外的领先地位,而且N5P还将拥有世界上最大的晶体管密度,并提供更高的性能。

当我接触到我们的技术路线图后,我可以肯定地说,台积电在这一领域有着多年的开拓和创新经验,我们将继续缩小单个晶体管面积,并进一步提高其密度。

随着我们的制程工艺进入到新的节点,您将在未来几个月和几年中看到更多我们在芯片工艺方面的消息。

三、如何解决系统密度?

除了解决单个晶体管的密度问题,我们还需要解决系统密度。

从CPU和GPU的经典计算任务中可以看出,现代芯片的晶体管时钟速度极快,接近5千兆赫甚至更高。实际上,这些计算任务所面临的核心挑战是保持CPU和GPU内核数据的供应。

虽然这是典型的软件问题,但现代线程架构和方法已经直接将性能瓶颈置于硬件层面。我们终于看到了大数据分析和人工智能时代内存缓存的局限性。

为了满足现代快速CPU、GPU和专用AI处理器的需求,我们除了要为内核处理器提供更高宽带的数据之外,还必须提供在物理上更靠近请求数据(requesting the data)的内存,以改善内核延迟,这些都是设备级密度所提供的。当内存靠近逻辑内核配置时,系统可以实现更低的延迟、更低的功耗和更高的整体性能。

有些人可能认为这是系统级的问题,而不是设备技术的内在属性。这在过去可能是正确的,但现在芯片和系统之间定义的界限已经变得模糊,并且还会更模糊,最终将完全被消除。因为目前我们已经从设计技术协同优化(DTCO)时代,过渡到了系统技术协同优化(STCO)的时代。

四、封装技术影响AI的训练和推理

当今的高级封装技术能让内存更接近逻辑处理。通常情况下,逻辑内核通过独立的存储器芯片进行反馈,如DDR或GDDR等接口。

存储设备和逻辑内核之间的物理距离会增加延迟,从而限制性能。离散存储器的带宽也会受到限制,因为它们只提供有限的接口宽度。

此外,逻辑分立器和存储器的功耗也决定了设备的整体性能,尤其是在智能手机或loT设备等应用中,因为分立器件辐射热能的能力有限。

像机器学习的训练和推理等其他应用,也正在突破功率、带宽和延迟的界限。

人工智能通常被视为一种计算机问题,但AI有两个不同的方面:训练(机器学习)和推理。

任何AI系统要进行工作都必须先训练神经网络,而训练需要密集的计算操作,例如前馈和后向传播,其中逻辑核心会被馈送大量数据。逻辑内核的馈送速度越快,学习速度就越快,因此带宽在这一步至关重要。

训练神经网络的行为消耗了极大的能量,但通过封装逻辑核心和内存,我们可以大大降低AI训练的功耗,同时增加内存带宽。

AI推理是训练好的神经网络在现实世界中的应用,同时也利用了边缘计算。一旦你有一个训练好的神经网络,边缘设备就需要进行该训练,并在尽可能短的时间内执行任务。

五、台积电已推出先进封装技术

目前,台积电已经能通过先进的封装技术将逻辑内核与存储器紧密集成。

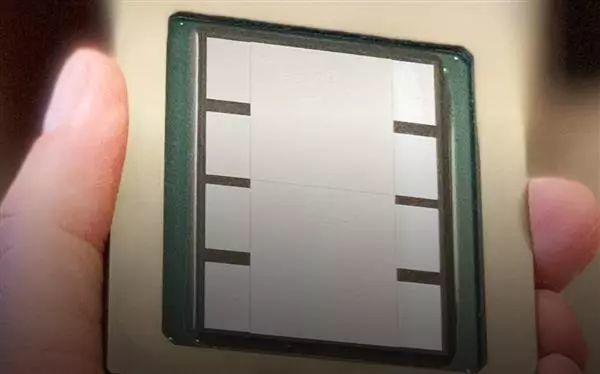

由于新的先进封装系统技术基于硅晶片,半导体和系统解决方案之间的界限很模糊。但台积电通过利用先进的封装技术,允许我们在集成到封装模块之前,将芯片堆叠在晶片上,或将晶片堆叠在晶片上。

这些先进的包装技术使芯片拥有更高的密度和性能,我们也将继续推动先进封装技术的创新。

摩尔定律是一个关于密度增加的观点。台积电将利用先进封装实现的系统级密度,进一步增加晶体管的密度。

台积电拥有许多提高晶体管密度的方法。其中一个可行的方法是利用由二维材料制程的晶体管代替硅,并作为沟道。通过使用这些新材料,我们在未来也许能在单片3D集成电路中堆叠多层晶体管,还可以在AI边缘引擎上的GPU再添加一个CPU。

摩尔定律并没有消亡,我们还有许多不同的途径可以继续提升芯片密度。

文章来源:TSMC

内容声明:除原创作品外,本平台所使用的文章、图片、视频及音乐属于原权利人所有,因客观原因,或会存在不当使用的情况,如部分文章或文章部分引用内容未能及时与原作者取得联系,或作者名称及原始出处标注错误等情况,非恶意侵犯原权利人相关权益,敬请相关权利人谅解并与我们联系及时处理,共同维护良好的网络创作环境。