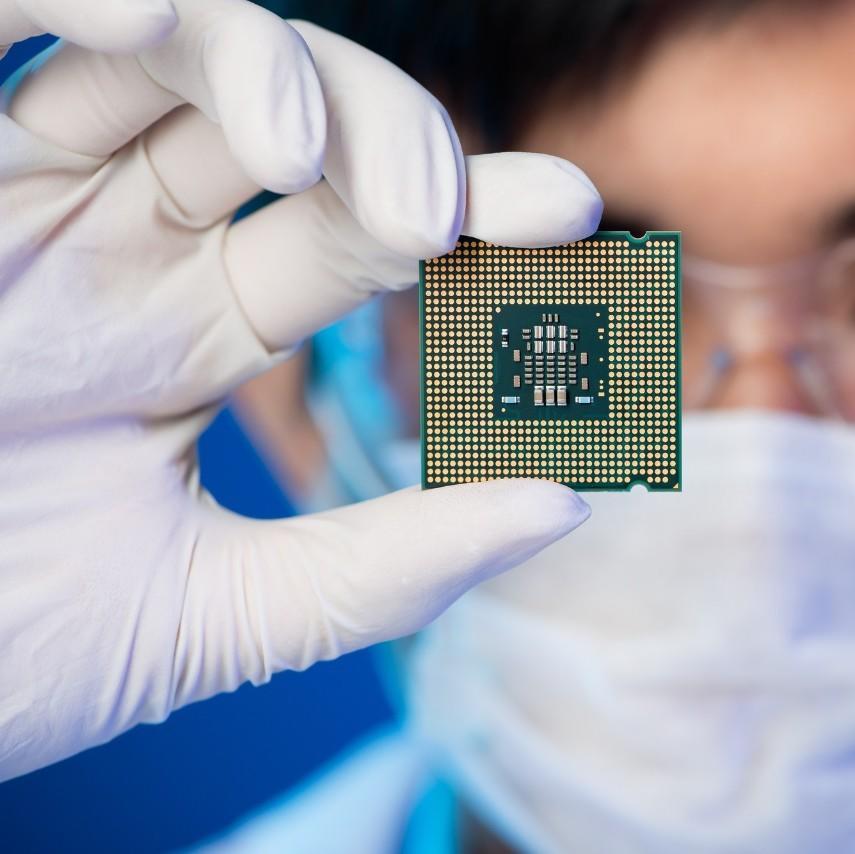

28日,有多家媒体报道了中国科研人员实现了3nm半导体工艺的突破性进展,香港《南华早报》称中科院微电子所团队的殷华湘等人研究出了3nm晶体管,相当于人类DNA链条宽度,这种晶体管解决了玻尔兹曼热力学的限制。

在中国半导体芯片正在被美国卡脖子的今天,国内科研人员实现3nm晶体管技术具有重要意义,南华早报在文章中也提到了该技术的意义——过去我们只能看着别人竞赛,现在可以参与这场竞赛了。

不过这个技术具体如何呢?找了下,南华早报的新闻源是中科院微电子所的通告,官方介绍的内容如下:

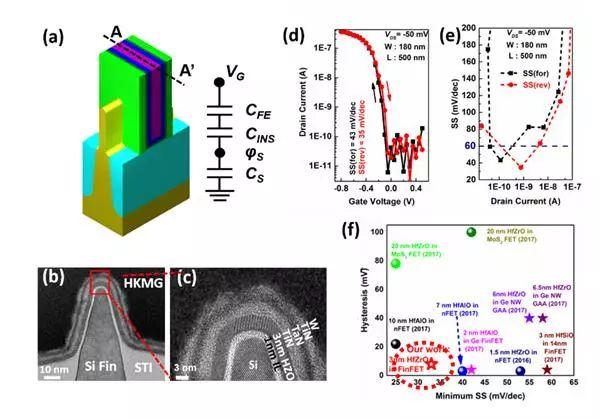

现有硅基晶体管受玻尔兹曼热力学限制,室温下亚阈值摆幅SS≥60mV/dec,阻碍了工作电压的继续降低。当集成电路技术进入5纳米及以下节点,随着集成度的持续增加,在维持器件性能的同时面临功耗急剧增加的严重挑战。

先导中心殷华湘研究员的团队在主流后HKMG FinFET集成工艺的基础上,通过材料工艺优化和多栅器件电容匹配设计,结合高质量低界面态的3纳米铪锆金属氧化物薄膜,研制成功性能优异的NC-FinFET器件,实现了SS和阈值电压回滞分别为34.5mV/dec和9mV的500纳米栅长NC-FinFET器件,以及SS和阈值电压回滞分别为53mV/dec和40mV的20纳米栅长NC-FinFET器件。

其中,500纳米栅长NC-FinFET器件的驱动电流比常规HfO2基FinFET器件(非NC-FinFET)提升了260%且电流开关比(Ion/Ioff)大于1×106,标志着微电子所在新型NC-FinFET器件的研制方面取得了重要进展。

上述最新研究结果发表在国际微电子器件领域的顶级期刊《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2019.2891364),并迅速受到国际多家研发机构的高度关注。

该项集成电路先导工艺的创新研究得到国家科技重大专项02专项和国家重点研发计划等项目的资助。

图1 (a)负电容FinFET基本结构;(b-c)三维器件沟道结构与铁电HZO膜层结构;(d-e)器件I-V与SS特性;(f)最新器件性能国际综合对比(SS与回滞电压越小越好)

图1 (a)负电容FinFET基本结构;(b-c)三维器件沟道结构与铁电HZO膜层结构;(d-e)器件I-V与SS特性;(f)最新器件性能国际综合对比(SS与回滞电压越小越好)

官方通报里用词要严谨的多,提到的3nm实际上说的是3nm氧化物薄膜的厚度,没有确定说是3nm工艺,不过这个技术也确实是用于5nm节点之后的工艺中。

不过这个所谓的负电容技术还是学术研究,南华报道中提到了殷华湘表示该技术具备应用实力,但是殷华湘也提到了这个技术距离商业化应用还有数年时间,团队还在致力于解决材料及质量控制等问题。

简单来说,这次的国产突破3nm工艺报道依然是一项重要的学术进展,但在半导体工艺上这样的例子太多了,除非能很快量产并且具备更好的性能或者更低的成本,否则这些工艺很难取代现在的半导体技术。

港媒相关报道:

中国3纳米晶体管研发获突破

在芯片前沿发起正面竞争

5月28日报道港媒称,内地的科学家说,他们已经研发出一种晶体管,这种晶体管将大大增强芯片的性能,并大幅降低它们的能耗。

据香港《南华早报》网站5月27日报道,现如今,市场上最先进的计算机芯片使用7纳米晶体管。中国科学院微电子研究所微电子设备与集成技术领域的专家殷华湘说,他的团队已经研发出3纳米晶体管——相当于一条人类DNA链的宽度,在一个指甲盖大小的芯片上能安装数百亿个这种晶体管。

殷华湘说,晶体管变得越小,芯片上就能安装越多的晶体管,这会让处理器的性能显著提升。晶体管是处理器的基本部件。殷华湘说,用3纳米晶体管制造的处理器将会增加计算速度,并降低能耗。比如一位智能手机用户可以整天玩需要大量计算能力的游戏,却不需要为电池重新充电。

殷华湘说,他的团队还必须克服一些重大障碍。他们的研究成果本月部分发表在同行评议杂志《电气与电子工程师协会电子器件通讯》上。其中一个障碍是“波尔兹曼暴政”。路德维希·波尔兹曼是19世纪的奥地利物理学家。“波尔兹曼暴政”描述的是有关电子在一个空间中的分布问题。对芯片研发者来说,这意味着随着更多较小的晶体管安装到芯片上,晶体管所需电流产生的热量将烧毁芯片。

报道称,物理学家已经为这个问题提供了解决办法。殷华湘说,他的团队使用一种称为“负电容”的方法,这样他们能用理论上所需最小电量的一半电量来为晶体管提供电力。这种晶体管实现商业应用可能要花几年时间。该团队正在进行材料和质量控制方面的工作。

殷华湘说:“这是我们工作中最激动人心的部分。这不仅是实验室中的又一项新发现。它有着实际应用的巨大潜力。而我们拥有专利。”

报道称,殷华湘说,这项突破将让中国“在芯片研发的前沿同世界头号角色进行正面竞争”。他说:“在过去,我们看着其他人竞争。现在,我们在同其他人竞争。”

据报道,中国还在研发一种原子大小(0.5纳米)的晶体管,而其他国家已经加入将3纳米晶体管投入市场的竞赛。

韩国三星公司说,它计划到明年上半年完成3纳米晶体管的研发。三星说,同7纳米技术相比,用它的3纳米晶体管制造的处理器只需用一半的电力,性能却会提高35%。三星没有说它预计这些芯片将于何时投产。

内容声明:除原创作品外,本平台所使用的文章、图片、视频及音乐属于原权利人所有,因客观原因,或会存在不当使用的情况,如部分文章或文章部分引用内容未能及时与原作者取得联系,或作者名称及原始出处标注错误等情况,非恶意侵犯原权利人相关权益,敬请相关权利人谅解并与我们联系及时处理,共同维护良好的网络创作环境。