一说到2D或者3D,总是让人想到视觉领域中的效果,然而在半导体领域,3D技术带来的革命更叹为观止,早些年的FinFET和3D NAND只是个开始。从去年12月初英特尔公布新架构路线,到1月初CES 2019上拿出M.2 SSD大小的整台电脑,这样的速度,你不得不更上!

到底是什么决定着产品质的飞越,销量徘徊不前的PC到底路在何方?英特尔在此次CES上给了大家答案和思考。

“早”在2011年年中,英特尔推出了向空间要性能的Tri-Gate 3D晶体管技术,成为LSI取代电子管之后,半导体制程革命的新标志。该技术就是今天已经广为各大半导体厂商所采用的FinFET。

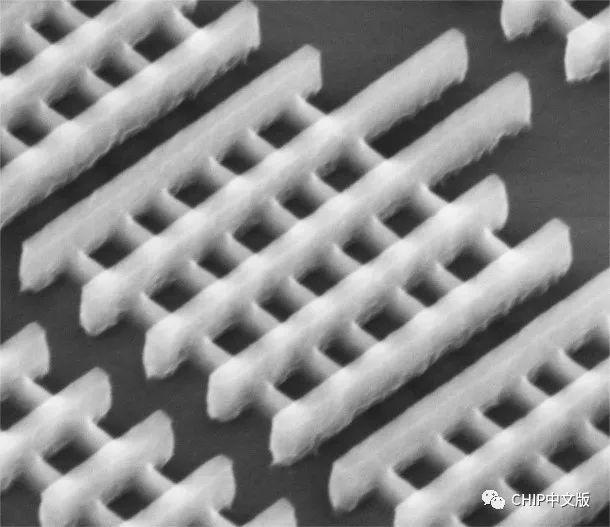

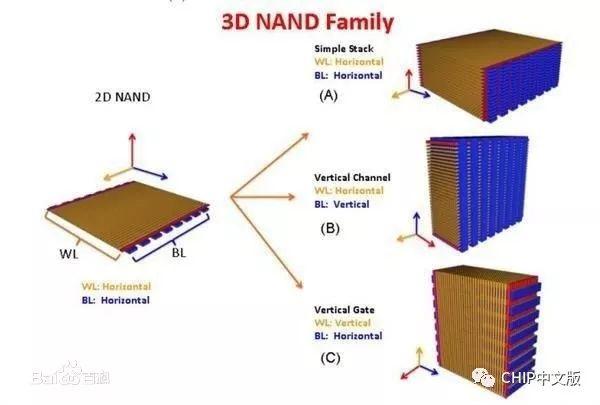

从2013年开始,多家主流的Flash厂商开始陆续推出3D NAND产品,最早推出该类产品的三星称之为V-NAND。与该技术普及相伴的是MLC向高堆叠TLC的技术演进,SSD进入寻常百姓家。

在这股浪潮中,英特尔/美光并不是十分积极,直到2015年才少量推出了使用相对独特的浮栅技术的3D NAND产品。真正的大招是他们同时宣布,2017年初正式推出成品的3D XPoint技术,英特尔称之为Optane(傲腾),比单纯的3D NAND只讲求容量增加,更多了一重性能(速度、延迟、寿命)的大幅提升。

可以说,半导体业界近年来每次大的技术飞越,都与3D化——从平面向空间要增长密不可分。而其中,英特尔的角色都是那么的微妙和关键。

刚刚公布就接近产品化的3D封装技术Foveros,将用多么“了不起(Foveros希腊语含义)”的成就改变半导体产业呢?

制程制程,制程是什么?无论是英特尔推演在的14nm、刚刚宣布2019年进入的,还是TSMC于去年下半年开始量产7nm,简单的描述是线宽,是晶片组成的半导体里弄中的道路宽度。路窄不是问题,关键是一方面要能保证车辆正常通行,另一方面还要防止路两侧房间不会隔路“相望”。英特尔不断的14nm制程优化过程,就是路不变窄的情况下,尽可能盖上更多的房间、住下更多的晶体管。同理,7nm的马路虽窄,但若不能很好地隔离不同“房间”间的干扰,房间的实际面积或距离,并不能随同制程改进而缩小,也就是晶体管密度没有增加,一切都等于白搭。

虽然FinFET技术已经完全普及,但是由于大多数CPU或SoC内部结构复杂、同时具有电气性能差异巨大的众多功能模块,FinFET技术只能实现单个晶体管,或者说栅极的空间布局,晶体管本身无法实现多层堆叠,即3D化。在这种情况下,CPU和SoC只能基于单片晶圆生产,同等制程情况下,对应DIE的面积反映出晶体管的数量,间接地呈现芯片性能。这也是摩尔定律已死的理论根源。

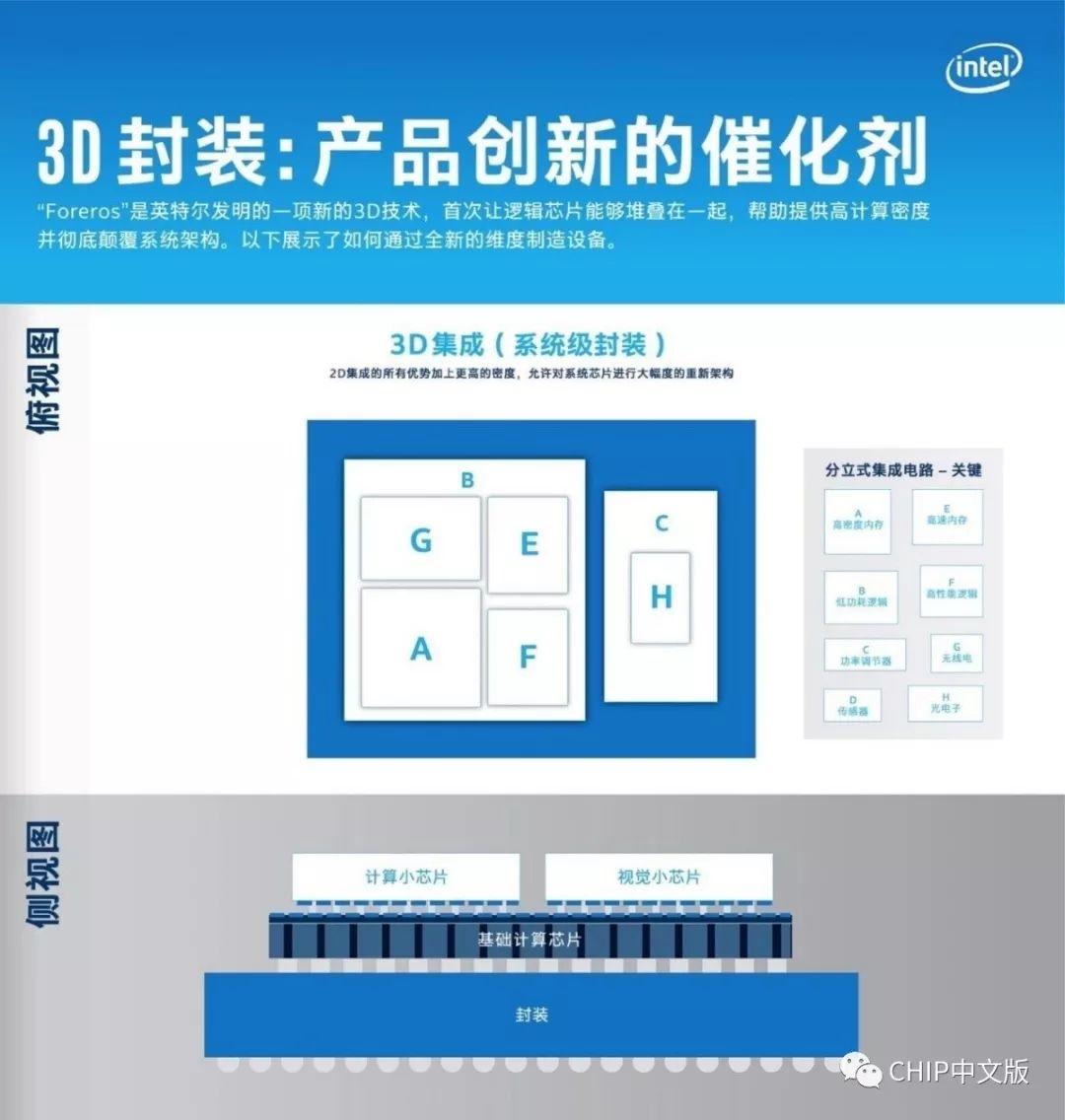

3D封装技术,在这里起到了革命性的作用,下面的故事有点像立体种植,把从面积要的产能改为向空间要。

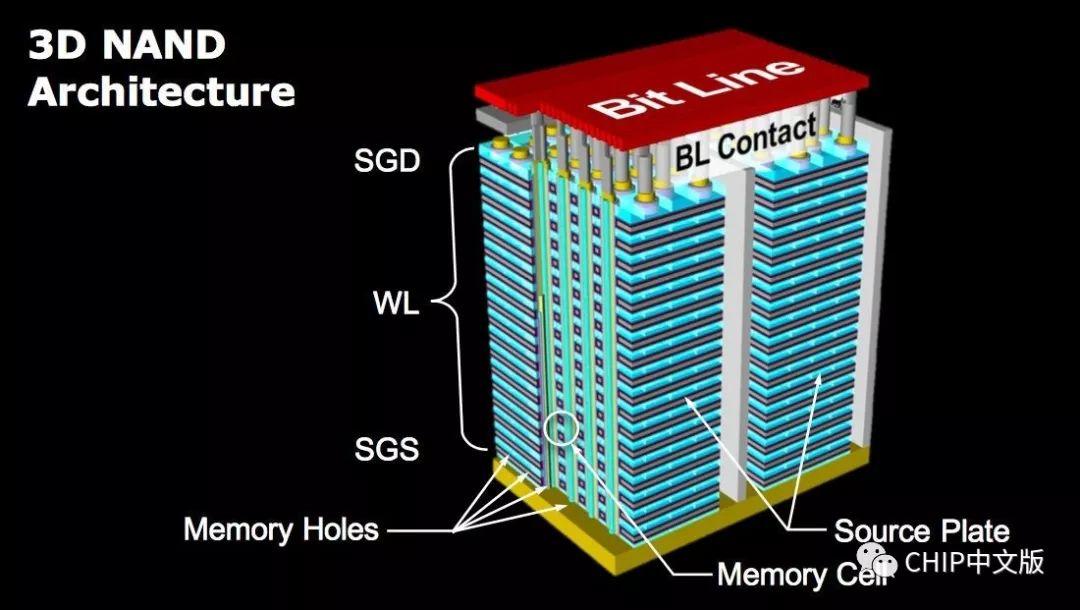

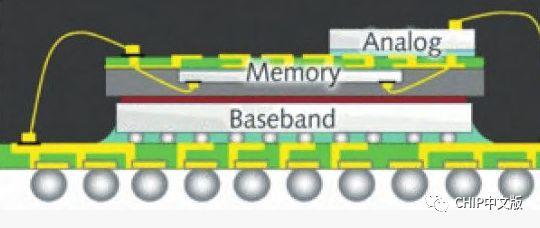

立体种植晶体管,对不起,暂时还不能。3D封装说得很清楚,就是在空间中而不是平面化封装多个芯片。也许你会说,这有什么新鲜的,芯片堆叠技术不是老早之前就被广泛使用了么,无论是DRAM还是NAND,都已广泛采用堆叠技术,特别是NAND已经从128层甚至更多层迈进。而智能手机所使用的SiP芯片,也是将SoC与DRAM堆叠在一起的。

DRAM/NAND堆叠相对简单,由于各层半导体功能特性相同,无论是地址还是数据,信号可以纵穿功能完全相同的不同楼层,就像是巨大的公寓楼中从底到顶穿梭的电梯。存储具有Cell级别的高度相似性,同时运行频率相对不高,较常采用这种结构。

SoC和DRAM芯片的堆叠,采用了内插器或嵌入式桥接器,芯片不仅功能有别,而且连接速度高,这样的组合甚至可以完成整个系统功能,因此叫SiP(System in Package)更准确。SiP封装足够小巧紧凑,但是其中功能模块十分固定,难以根据用户需要自由组合IP模块,也就是配置弹性偏低。

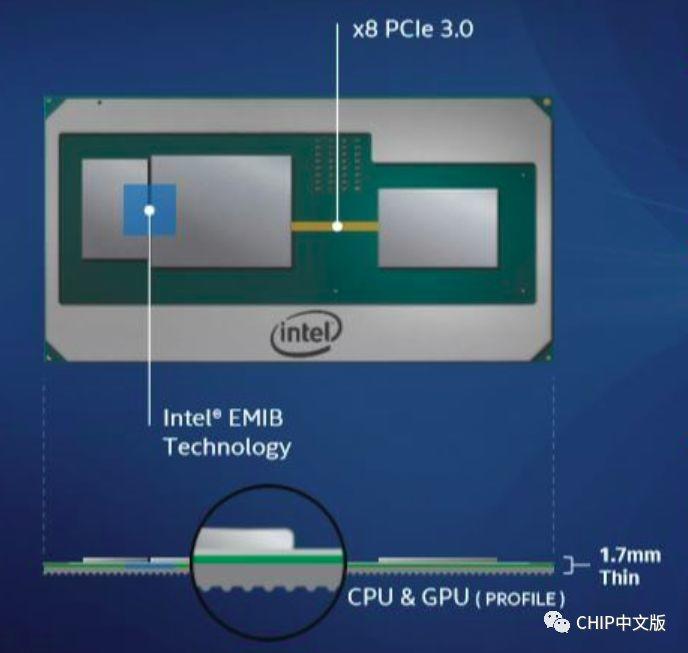

在去年年初,英特尔推出Kaby Lake-G令人眼前一亮,片上集成AMD Vega GPU和HBM2显存的Kaby Lake-G让EMIB(嵌入式多芯片互连桥接)封装技术进入人们眼帘,而该技术还只是2D封装,也就是所有芯片在一个平面上铺开。

现在,英特尔已准备好将3D封装引入主流市场,也就是Foveros。Foveros 3D封装将多芯片封装从单独一个平面,变为立体式组合,从而大大提高集成密度,可以更灵活地组合不同芯片或者功能模块。

多IP组合灵活(异构),并且占用面积小、功耗低,是Foveros最显著的特点。特别是结合上英特尔10nm制程,摩尔定律从晶体管密度(2D)到空间布局(3D)两个维度得到延续。

Lakefield是英特尔在CES 2019上披露的全新客户端平台的代号,该平台支持超小型主板,有利于 OEM 灵活设计,打造各种创新的外形设计。该平台采用英特尔异构 3D封装技术,并具备英特尔混合CPU架构功能。借助Foveros,英特尔可以灵活搭配3D堆叠独立芯片组件和技术IP模块,如I/O和内存。混合CPU架构将之前分散独立的CPU内核结合起来,支持各自在同一款10nm产品中相互协作:高性能Sunny Cove内核与4个Atom内核有机结合,可有效降低能耗。英特尔宣布预计将于2019年下半年推出使用这种全新3D堆叠技术的产品。

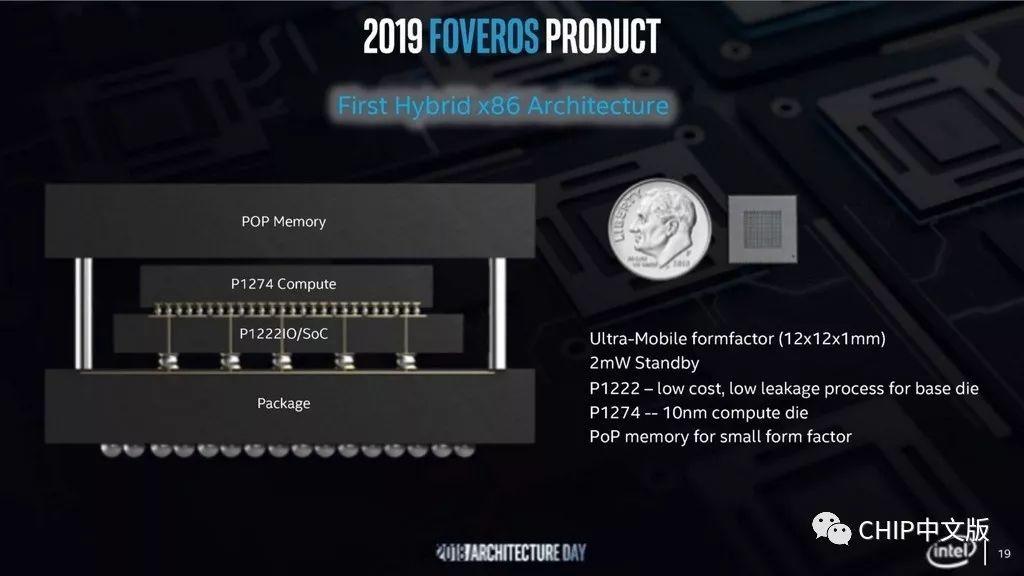

这颗Foveros 3D封装技术打造的硬币大小的芯片,从下至上,依次是封装基底(Package)、底层芯片(Bottom Chip)、中介层(Active Interposer,中介层上的上层芯片可以包括各种功能,如计算、图形、内存、基带等。中介层上带有大量特殊的TSV 3D硅穿孔,负责联通上下的焊料凸起(Solder Bump),让上层芯片和模块与系统其他部分通信。

该芯片封装尺寸为12mm×12mm、厚1mm,而内部3D堆叠封装了多个模块:基底是P1222 22FFL(22nm改进工艺)工艺的I/O芯片;之上是P1274 10nm制程计算芯片,内部整合了一个Sunny Cove高性能核心、4个Atom低功耗核心;PoP整合封装的内存芯片。据称,整颗芯片的功耗最低只有2mW,最高不过7W,注意,这可是高性能的x86架构芯片,不是ARM的哟!

围绕这颗芯片制成的电脑主板尺寸缩小到一块M.2规格SSD大小,要知道此前Core m SoC平台主板的面积小1/2以上。

同时Sunny Cove 高性能核心将提供用于加速 AI 工作负载的全新集成功能、更多安全特性,并显著提高并行性,以提升游戏和媒体应用体验,特别是其高级媒体编码器和解码器,可在有限功耗内创建4K视频流和8K内容。另外,从Ice Lake开始,英特尔承诺的直接集成Thunderbolt 3和支持Wi-Fi 6(802.11ax)等功能也将落地,全面增强连接性能。

此后,10nm技术将逐步拓展到桌面级产品领域、Foveros 3D封装的Lakefield,而至强可扩展(Xeon Scalable)平台(Ice Lake-SP)则将在2020年进行升级。

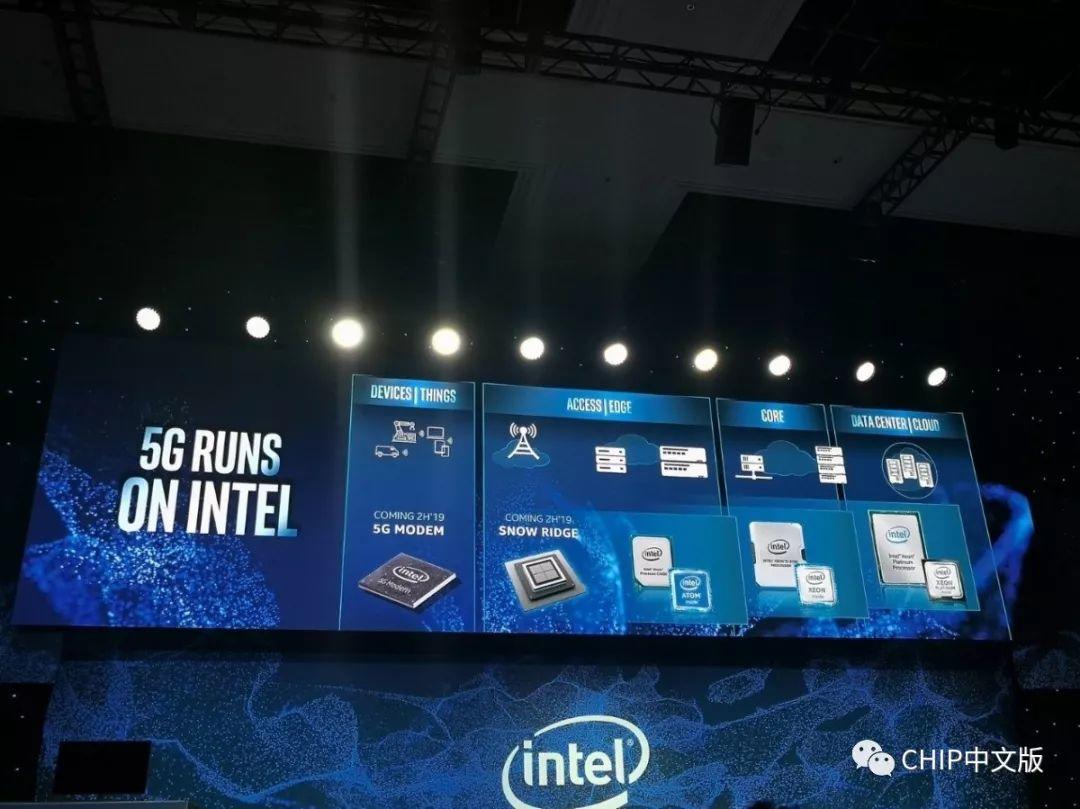

随着东京奥运会的临近,英特尔的5G技术也在加紧部署。其中代号为Snow Ridge的首款10nm 5G无线接入和边缘计算的网络系统芯片,将把英特尔的计算架构引入无线接入基站领域,从而充分让其计算功能在网络边缘进行分发。CES 2019上,英特尔展示了基于Snow Ridge平台的一款小型无线基站,整个设备的体积非常小巧,而这颗芯片示Snow Ridge也采用了Foveros 3D封装工艺,交付时间为今年下半年。

新制程与新封装,一直是英特尔称霸半导体领域的基石。2011年的22nm+Tri-Gate,2019年的10nm+Foveros,摩尔定律的世界依然宽广。

等待了数年,英特尔新技术将再次改变世界,起点仍将是集各领域发展前沿于大乘的PC领域。在可以预见的将来,AI加持的CPU仍将是核心计算单元,经过重新构建的CPU架构,无论是从Sunny Cove开始的新一代酷睿微架构,还是Lakefield所展现的混合CPU架构,都极大地平衡了性能与功耗,将高性能、小型化与长续航推向新的高度。在最新发布的一批9代酷睿处理器上,新的“F”后缀产品已经不再集成核显,与Ice Lake走向市场前后脚,英特尔回归独显市场的首款产品Arctic Sound也将上市,随后的13代产品Jupiter Sound更是再推翻番的性能。再加上本地连通的PCI-E 4.0、扩展连接的集成Thunderbolt 3,结合了5G和Wi-Fi 6的“永远在线”,存储上的Optane Memory及Optane SSD,无所不能的PC在英特尔技术的打造下正在浮出水面,PC的世界依然相当精彩。